COPYRIGHT IS NOT RESERVED BY AUTHORS. AUTHORS ARE NOT RESPONSIBLE FOR ANY LEGAL ISSUES ARISING OUT OF ANY COPYRIGHT DEMANDS AND/OR REPRINT ISSUES CONTAINED IN THIS MATERIALS. THIS IS NOT MEANT FOR ANY COMMERCIAL PURPOSE & ONLY MEANT FOR PERSONAL USE OF STUDENTS FOLLOWING SYLLABUS PRINTED NEXT PAGE. READERS ARE REQUESTED TO SEND ANY TYPING ERRORS CONTAINED, HEREIN.

# 5<sup>th</sup> Semester ETC ENGG. (COURSE CODE- BEC 1502)

# **Microprocessors (3-1-0)**

# Module-1

Introduction to Microprocessor: Intel 8085 Microprocessor: Architecture, pins & signals, Register organization, Timing & control unit, Instruction Timing & Execution, Instruction set of 8085, Memory & I/O Addressing, Assembly language programming using 8085 instructions set.

Module-2

Memory Interfacing: Interfacing EPROM &RAM Memories: 2764 and 6264. Stack &Subroutines: Stack, Subroutines, Restart, Conditional Call and Return Instructions, Advanced Subroutine Concepts. 8085 Interrupts: 8085 Interrupts, Vectored Interrupts, Restart as Software Instructions.

## Module-3

Microprocessor based system Developments Aids: Programmable peripheral Interface: 8255, Programmable DMA Controller: 8257, Programmable Interrupt Controller: 8259, Programmable Interval Timer: 8253.

# Module-4

Intel 8086 (16 bit): Introduction, pins & signal description, Architecture, Bus timing, minimum mode 8086, and maximum mode 8086, Multiprocessor: parallel processing, Instruction sets of 8086: Instruction formats, Addressing modes, Instruction set: data transfer instruction, arithmetic and logic instruction, program control instructions, Assembly language programming with 8086, iterative procedure, recursive procedure, parameter passing.

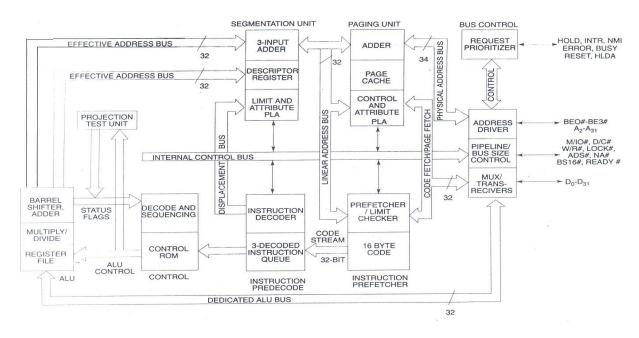

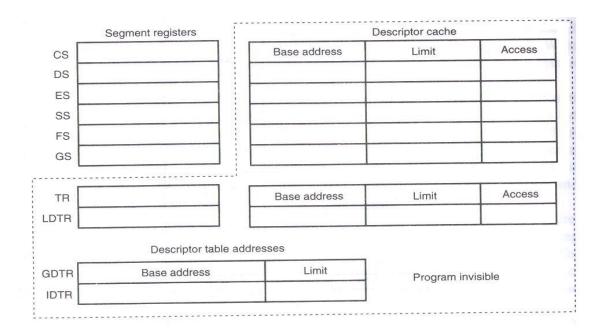

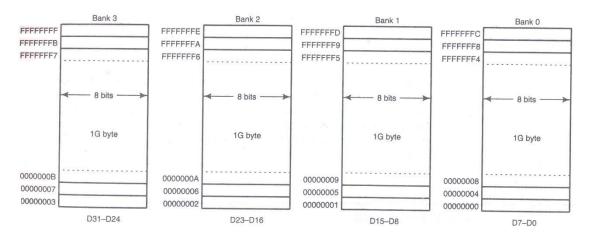

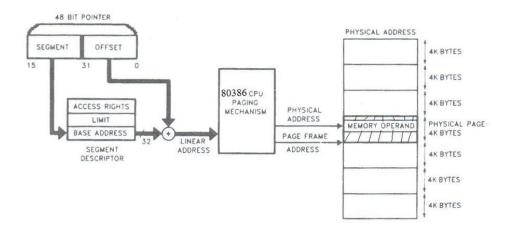

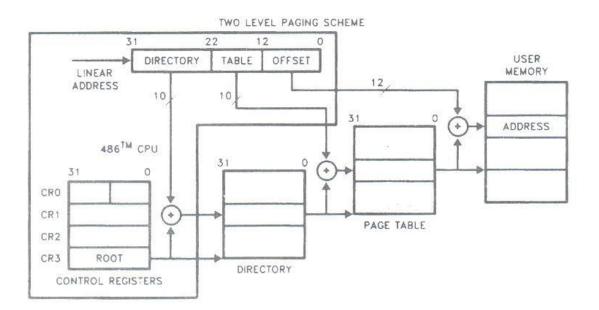

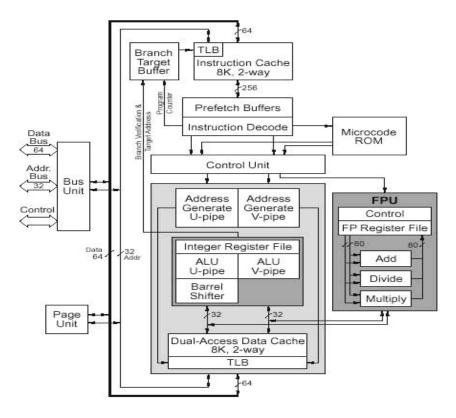

Intel 80386 and 80486: Architecture, Register Organization, Protected mode, Paging, Virtual mode.

Salient features of Pentium Processor.

Text books:

- Microprocessor Architecture, programming and applications with the 8085 by R.S. Gaonkar, Penram International, India.

- Microprocessors and Microcontrollers by N.Senthil Kumar, M.Saravanan, and S.Jeevananthan, Oxford University Press.

(12 Hours)

(8 Hours)

(10 Hours)

(10 Hours)

#### **MODULE-1**

**Introduction to Microprocessor**: Microprocessor is an electronic chip that functions as the central processing unit (CPU) of a computer. The microprocessor based systems with limited resources are called as microcomputers. Now-a-days microprocessors are found in almost all electronic machines and appliances in its different form. Some common devices using microprocessors are computer, printers, automobiles, washing machines, microwave ovens, mobile phones, fax machines, Xerox machines and advanced instruments like radar, satellites, flights etc.

Almost all microprocessors use the basic concept of "stored program execution". By this concept, programs are stored sequentially in memory locations. The microprocessor will fetch the instructions one after the other and execute them in its arithmetic and logic unit. So it is necessary for the user to know about the internal resources and features of the microprocessor. The programmers must also understand the instructions that a microprocessor can support. Every microprocessor will have its own associated set of instructions and this list is given by all the microprocessor manufacturers. Programs are written using mnemonics called the assembly level language and then they are converted into binary machine level language. This conversion can be done manually or using an application called assembler.

In general, the programs are written by the user for a microprocessor to work with real world data. These data are available in many forms and are from many sources. A microprocessor based system need a set of memory units, set of interfacing circuits for inputs and a set of interfacing circuits for outputs. All circuits put together along with microprocessor are called as microcomputer system. The physical components of the microcomputer system are in general called as hardware. The program which makes this hardware useful is called as software.

### **Origin of Microprocessor**

The breakthrough in transistor technology led to the introduction of minicomputers of the 1960s and the personal computer revolution of the 1970s. Microprocessors evolution is categorized into five generations i.e. first, second, third, fourth, and fifth generations.

### First Generation (1971-73)

The microprocessors that were introduced in 1971 to 1972 were referred to as the first generation systems. Intel Corporation introduced 4-bit 4004 at 108 kHz, the first microprocessor in 1971, co-developed by Busicom, a Japanese manufacturer of calculators. In 1972, Intel made the 8-bit 8008 and 8080 microprocessors.

#### Second Generation (1974-78)

The second generation marked the beginning of very efficient 8-bit microprocessors. Some of the popular processors are Motorola's 6800 and 6809 and Intel's 8085, Zilog's Z80. The distinction between the first and second generation devices is primarily the use of newer semiconductor technology to fabricate the chips. They were manufactured using NMOS technology.

Third Generation (1979-80)

Introduced in 1978, dominated by Intel's 8086 and the Zilog Z8000, which were 16-bit processors, have 16-bit arithmetic and pipelined instruction processing.

Fourth Generation (1981-95)

Intel introduced 32 bit processor, 80386 and Motorola 68020/68030. Fabricated using low-power version of the HMOS technology called HCMOS.

Fifth Generation (1995 till date)

Chips carry on-chip functionalities and improvements in the speed of memory and I/O devices. Design surpassed 10 million transistors per chip. Introduction of 64-bit processors.Intel leads the show with Pentium, Celeron and dual and quad core processors working with up to 3.5GHz speed.

### Intel 8085 Microprocessor

### Introduction

8085 is an eight bit microprocessor of Intel Corporation, usually called as a general purpose 8-bit processor. It is upward compatible with microprocessor 8080, which is the earlier product of Intel. Several faster versions of 8085 microprocessor are 8085AH, 8085AH-1, and 8085AH-2.

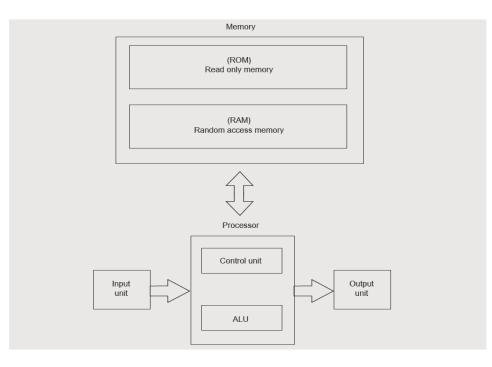

A microprocessor system consists of three functional blocks: central processing unit (CPU), input and output units, memory units as shown in figure1.1. The central processing unit contains several registers, arithmetic logic unit (ALU) and control unit.

Figure 1.1: Microprocessor System

Microprocessor is an integrated chip that functions as the central processing unit of a computer. The microprocessor basically performs

- Memory Read: Accept data (instruction) from memory.

- Memory Write: Send data to memory.

- I/O Read: Accept data from input device.

- I/O Write: Send data to output device.

- Controls timing of instruction flow.

Memory includes ROM (read only memory) and RAM (random access memory or read write memory). The memory

- Stores instructions and data.

- Provides the instructions and data to processor.

- Stores results.

The input devices enter instructions and data to processor. The input device includes Key-Board (Hexadecimal / ASCII), Switches, and Analog-to-Digital (A/D) convertor.

The output devices accept data from processor. This includes LED (Light Emitting Diode) display, LCD (Liquid Crystal Diode) display, CRT (Cathode Ray Tube) Screen.

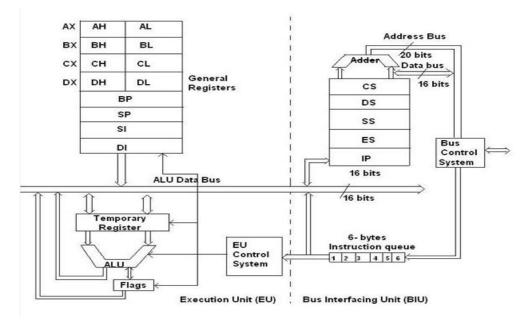

## Architecture

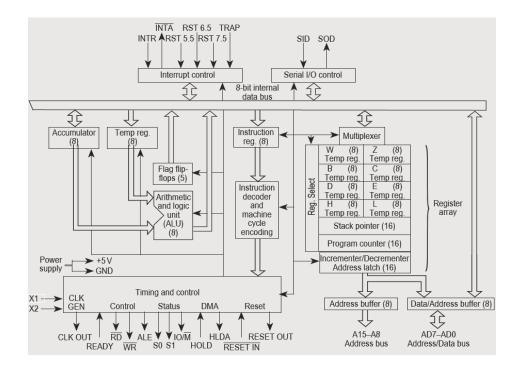

The internal block diagram of 8085 is shown in figure 1.2. It is a 40 pin IC package and uses +5V for power. It can run at a maximum frequency of 3MHz. It is a 8-bit processor which has a data bus of 8-bits wide. It has addressing capability of 16-bit. That is it can address  $2^{16} = 64K$  Bytes of memory (1Kbyte =1024 byte).

The architecture of 8085 processor consists of five functional units: Arithmetic and logic Unit, General purpose registers, Special Purpose Registers, Instruction register/decoder and Timing and control unit.

Figure 1.2: Architecture of 8085

### **Register Organization**

The register organization of 8085 is shown in figure 1.3.

| Accumulator A (8)       | Flag register             |  |  |

|-------------------------|---------------------------|--|--|

| B (8)                   | C (8)                     |  |  |

| D (8) E (8)             |                           |  |  |

| H (8)                   | L (8)                     |  |  |

| Stack pointer (SP) (16) |                           |  |  |

| Program                 | counter (PC) (16)         |  |  |

| Data bus                | Address bus               |  |  |

| 8 lines (bidirectional) | 16 lines (unidirectional) |  |  |

Figure 1.3: Register Organization of 8085

Registers: The 8085 has six general purpose registers to store 8-bit data. They are identified as B, C, D, E, H and L. They can be combined as register pairs: B-C, D-E, and H-L to store and perform 16-bit operations.

The 8085 special purpose registers are the Accumulator, Flag register, Program Counter (PC) and Stack Pointer (SP).

Accumulator: This is an 8 bit register that is part of arithmetic and logical unit (ALU). This is used to store 8-bit data and perform arithmetic and logical operations. The result of an operation is stored in the accumulator.

Program Counter (PC): This is a 16-bit register, which always points to the address of next instruction to be fetched.

Stack Pointer (SP): This is a 16-bit register that points to a memory location in R/W memory, called as stack.

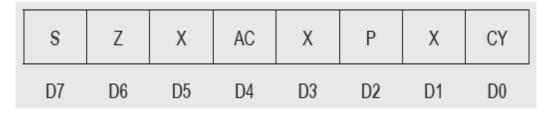

Flags: The ALU includes five flip-flops, which are set or reset after an operation according to data conditions of result in the accumulator. They are called as Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags .The flag register format of 8085 is shown in figure 1.4.

Figure 1.4: Flag Register Format of 8085

- Z-Zero: The zero flag is set if the result is zero, otherwise it is reset.

- CY-Carry: If an arithmetic operation results in a carry, the carry flag is set otherwise it is reset.

- S-Sign: The sign flag is set if bit D7 of the result is one, otherwise it is reset.

- AC- Auxiliary Carry: In a BCD arithmetic operation, when a carry results from digit D3 and passes on to digit D4, the AC flag is set.

- P-Parity: If the result has an even number of 1's, the parity flag is set. For odd number of 1's, the flag is reset.

Two additional 8-bit temporary registers W and Z are included in the register array. They are not programmable.

### The ALU (arithmetic and logic unit)

The arithmetic logic unit of 8085 performs addition, subtraction, increment, decrement and comparison arithmetic operation and logical operations such as AND, OR, exclusive-OR, complement. The ALU includes the accumulator, the temporary register, the arithmetic logic circuits, and five flip-flops. The temporary register is used to hold data during arithmetic logic operation. The result is stored in accumulator, and flags are set or reset according to result of operation.

The 8085 is also called accumulator oriented processor as one of the data in the ALU operation is stored in the accumulator. The other data may be in memory or in register.

### **Timing and Control unit**

The timing and control unit synchronizes all microprocessor operations with clock and generates control and status signals (RD, WR) for communication between microprocessor and peripherals.

### Instruction Register and Decoder

The Instruction register/decoder is an 8-bit register that is part of the ALU. When an instruction is fetched from memory, it is loaded in the instruction register. The decoder decodes the instruction. The instruction register is not programmable.

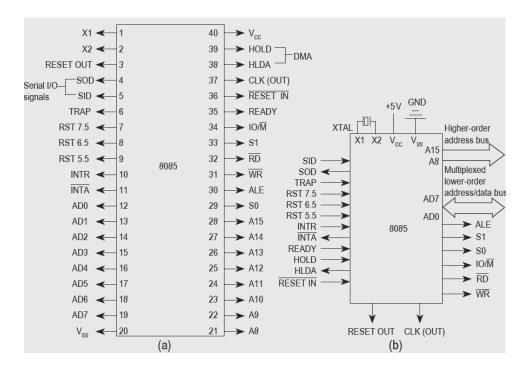

### **Pins and Signals**

Intel 8085 has 40 pins, operates at 3MHz clock and requires +5V for power supply. The pin diagram of 8085 is shown in figure 1.6. The signals can be classified into six groups i.e. Address Bus, Data Bus, Control and Status Signals, Power supply and System Clock, Externally Initiated Signals, and Serial I/O signals.

### Address and Data Buses

The 8085 has 16 bit (A15-A0) address lines which are unidirectional and 8-bit (D7-D0) data lines which are bidirectional.

A8 - A15 (Output-3 state: higher order address bus): The most significant 8 bits of the memory address or the 8 bits of the I/O addresses, tri-stated during Hold and Halt modes.

AD0-AD7 (Input/output- 3 state: multiplexed address/data bus): Lower 8 bits of the memory address (or I/0 address) appear on the bus during the first clock cycle of a machine state. It then becomes the data bus during the second and third clock cycles. Tri- stated during Hold and Halt modes.

### **Control and Status Signals**

ALE (Output) Address Latch Enable:

This output signal indicates the availability of the valid address on the address/data lines. It occurs every time during the first clock cycle of the 8085 machine cycle operation. It is used to latch the low order address from multiplexed bus and generate a separate address (A7-A0).

RD (Output- 3 state) READ:

This is a Read control signal (active low). This indicates that the selected memory or I/O device is to be read and data are available on the data bus.

### WR (Output- 3state) WRITE:

This is a Write control signal (active low). This indicates that the data on the data bus is to be written into the selected memory or I/O location.

IO/M (Output: 3 state ):

This is a status signal used to differentiate between I/O and memory operation. When it is high, it indicates an I/O operation. When it is low, it indicates a memory operation.

SO, S1 (Output): These are status signals and identify various operations (Figure 1.5).

| <b>S</b> 1 | <b>S</b> 0 | States |

|------------|------------|--------|

| 0          | 0          | Halt   |

| 0          | 1          | Write  |

| 1          | 0          | Read   |

| 1          | 1          | Fetch  |

### Figure 1.5: 8085 Status Signals

## **Externally initiated signals**

HOLD (Input):

It is an active high signal used in the direct transfer of data between a peripheral device and memory locations. This type of data transfer is called as direct memory access (DMA).During this transfer, the microprocessor loses control over the address and data buses and these buses are tri-stated.

Logic 1 on the Hold pin indicates that another controller, generally the DMA controller, is requesting the use of the address and data buses.

HLDA (Output): Hold Acknowledge

This is an active high signal, and acknowledges HOLD request.

INTR (Input): Interrupt Request

The INTR is used as a general purpose interrupt.

INTA (Output): Interrupt Acknowledge

This is an active low signal and is used to acknowledge an interrupt.

RST 7.5, RST 6.5, and RST 5.5: Restart Interrupts (input):

These three are hardware vectored interrupt signals.

TRAP (Input) :

This is a non-maskable interrupt and has highest priority.

RESET IN (Input):

When this goes low, the Program Counter is set to zero (0000H), the buses are tri-stated and reset the 8085.

**RESET OUT (Output):**

This indicates that 8085 is being reset. This can be used to reset other devices.

### **Power supply and Clock Frequency**

X1, X2 (Input):

A Crystal or R-C or L-C network is connected to these two pins. The crystal frequency is internally divided by two to give the operating system frequency.So, to run the microprocessor at 3 MHz, a clock running at 6 MHz should be connected to the X1and X2 pins.

CLK (Output): Clock Output:

This output clock pin is used to provide the clock signal for other devices.

Power supplies:Vcc : +5 V supply; Vss : Ground Reference

### Serial I/O Signals

SID and SOD implement serial data transmission.

SID (Input):

Serial input data line. The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

SOD (output):

Serial output data line. The accumulator bit 7 output on SOD line by the SIM instruction.

### Instruction Timing and Execution:

An instruction is a command to a microprocessor to perform a specific task on data. Each instruction consists of two parts: one is operation code (OPCODE), and second one is Operand.

Instruction Cycle:

It is defined as the time taken by the processor to complete fetch and execution of an instruction. Instruction cycle consists of both fetch cycle and execute cycle. Instruction cycle consists of 1 to 6 machine cycles.

Fetch Cycle:

It is defined as the time taken by the processor to fetch an operation code from memory.

Execution Cycle:

It is defined as the time taken by the processor to decode and execute an instruction.

Machine Cycle:

The time required to complete one operation of accessing memory, I/O. or acknowledging an external request. The machine cycle consists of 3 to 6 T-states.

T state:

The T state is equal to one clock period. The T state is defined as one sub division of an operation performed in one clock period.

8085 Machine Cycles

The 8085 microprocessor has 5 (Five) basic machine cycles. They are Opcode Fetch Cycle (4T), Memory Read Cycle (3 T), Memory Write Cycle (3 T), I/O Read Cycle (3 T), and I/O Write Cycle (3 T). In Opcode Fetch Cycle processor get a Opcode from memory. The processor read data from memory in Memory Read Cycle. In Memory Write Cycle, the data is stored in memory. The processors get data from input device in I/O Read Cycle and send data to output device in I/O Write Cycle.

Timing Diagram:

The timing diagram of an instruction is obtained by drawing the binary levels on the various signals of 8085. It is drawn with respect to the clock input of the microprocessor. It explains the execution of the instruction with the basic machine cycles of that instruction, one by one in the order of execution.

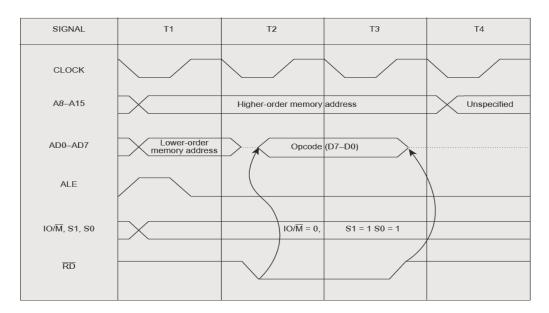

# Opcode Fetch Cycle (4T):

It is defined as the time taken by the processor to fetch an operation code from memory. The program counter places 16-bit memory address on the address bus. The 8085 sends memory read control signal to enable memory chip. The operation code from memory location is placed on the data bus. The operation code from data bus is stored in the instruction register to decode and execute.

Figure 1.6: Timing Diagram of Opcode Fetch Cycle

- At T1, the high order 8 address bits are placed on the address lines A8 A15 and the low order bits are placed on AD7–AD0. The ALE signal goes high to indicate that AD0 AD8 are carrying an address. At exactly the same time, the IO/M signal goes low to indicate a memory access operation.

- At the beginning of the T2 cycle, the low order 8 address bits are removed from AD7– AD0 and the processor sends the Read (RD) signal to the memory. The RD signal remains low (active) for two clock periods to allow for reading slow devices. During T2, memory places the operation code byte from the memory location on the lines AD7– AD0.

- During T3 the RD signal is Disabled (goes high). This turns off the output Tri-state buffers in the memory. That makes the AD7– AD0 lines go to high impedance state.

- During T4, the opcode is decoded by the processor and necessary action or control is initiated for the execution of the instruction fetched.

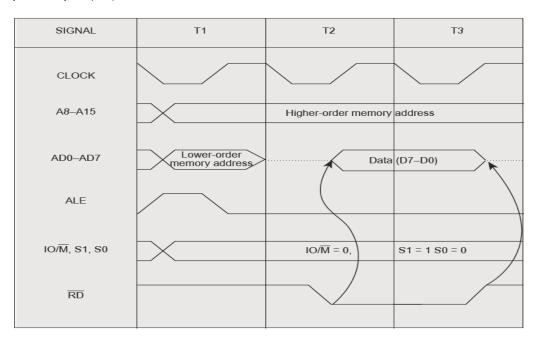

Memory Read Cycle (3 T) :

Figure 1.7: Timing Diagram of Memory Read Cycle

The memory read cycle is similar as the opcode fetch cycle except: It only has 3 T-states. The S0 signal is 0. S1 is set to 1.In memory read cycle processor read a data byte from memory.

## Instruction Set of 8085

An instruction is a command to a microprocessor to perform a specific task on data. The instruction set is the total number of instructions supported by processor.

Each instruction consists of two parts: one is operation code (OPCODE), and second one is Operand. The operation code specifies the type of operation to be performed. The operand is the data to be operated on. The operand includes 8-bit/16-bit data, an internal register, memory location, and 8-bit/16-bit address.

In the design of 8085, all the instructions, and registers are identified with a binary code.

| Code | Registers |

|------|-----------|

| 000  | В         |

| 001  | С         |

| 010  | D         |

| 011  | E         |

| 100  | Н         |

| 101  | L         |

| 110  | А         |

| 111  | Μ         |

| Code | Register Pair |

|------|---------------|

| 00   | B-C           |

| 01   | D-E           |

| 10   | H-L           |

| 11   | AF or SP      |

### Instruction Word Size

The word size of 8085 instruction can be

1-byte instruction: ADD B

The opcode and operand are in the same byte.

2-byte instruction: MVI A, 05H.

The first byte specifies opcode and second byte specify the operand.

3-byte instruction: LDA 2000H.

The first byte specifies opcode and the following two bytes specify 16-bit address.

#### Addressing Mode

The various techniques to specify data for instruction is called addressing mode.

Direct addressing: The address of the data is specified in the instruction itself. STA 2000H, IN 07H.

**Register addressing**: The operands are in general purpose register. MOV A, B, ADD B.

Register indirect addressing: The address of the operand is specified by register pair indirectly.

MOV A, M , ADD M.

Immediate addressing: The operand is specified within the instruction itself.MVI A,03H, ADI 12H.

**Implicit addressing**: The operand is in the accumulator. CMA, RAL, RAR.

The entire group of instructions is called the instruction set, and this determines the functionalities the microprocessor can perform.

The 8085 Instructions can be classified into five functional categories: Data Transfer (copy) operations, Arithmetic operations, Logical operations, Branching operations, and Machine-control operations.

### Data transfer instructions

This group of instructions copy data from a location called a source to another location called a destination without modifying the contents of the source. The various type of data transfer are:

Between registers: MOV B, D

Data byte to register/memory: MVI A, 45H, MVI M, 34H.

Between memory and register: LDA 2100H, STA 2400H.

Between I/O device and accumulator: IN 16H, OUT 12H.

### **Arithmetic instruction**

The arithmetic instructions are addition, subtraction, increment, and decrement.

### Addition

Any 8-bit number, or the content of a register, or the content of a memory location can be added to the content of accumulator. The sum is stored in the accumulator.

The DAD instruction adds 16-bit numbers in register pairs.

### Subtraction

Any 8-bit number, or the content of a register, or the content of a memory location can be subtracted from the content of accumulator. The result is stored in the accumulator. The subtraction is performed in 2's complement form.

| Mnemonics | Tasks performed on execution                    | Addressing<br>mode | Length of<br>the<br>Instruction | Example |

|-----------|-------------------------------------------------|--------------------|---------------------------------|---------|

| ADI 8-bit | Add immediate to accumulator                    | Immediate          | Two bytes                       | ADI 30H |

| ACI 8-bit | Add immediate to accumulator with carry         | Immediate          | Two bytes                       | ACI 4FH |

| SUI 8-bit | Subtract immediate from accumulator             | Immediate          | Two bytes                       | SUI 2AH |

| SBI 8-bit | Subtract immediate from accumulator with borrow | Immediate          | Two bytes                       | SBI 5CH |

| ADD R  | Add register content to accumulator                                    | Direct   | One byte | ADD C |

|--------|------------------------------------------------------------------------|----------|----------|-------|

| ADC R  | Add register content to accumulator with carry                         | Direct   | One byte | ADC E |

| SUB R  | Subtract register content from accumulator                             | Direct   | One byte | SUB B |

| SBB R  | Subtract register content and borrow from accumulator                  | Direct   | One byte | SBB C |

| DAD Rp | Add register pair to H and L registers                                 | Direct   | One byte | DAD B |

| INR R  | Increment register by 1                                                | Direct   | One byte | INR B |

| INX Rp | Increment register pair by 1                                           | Direct   | One byte | INX B |

| DCR R  | Decrement register by 1                                                | Direct   | One byte | DCR E |

| DCX Rp | Decrement register pair by 1                                           | Direct   | One byte | DCX D |

| ADD M  | Add memory content pointed by HL register pair to accumulator          | Indirect | One byte | ADD C |

| ADC M  | Add memory content pointed by HL register pair to accumulator          | Indirect | One byte | ADC E |

| SUB M  | Subtract memory content pointed by HL register pair from accumulator   | Indirect | One byte | SUB B |

| SBB M  | Subtract memory content pointed by HL pair and borrow from accumulator | Indirect | One byte | SBB C |

| INR M  | Increment a memory content pointed by HL register pair once            | Indirect | One byte | INR M |

| DCR M  | Increment a memory content pointed by HL register pair once            | Indirect | One byte | INR M |

| DAA    | Decimal adjust accumulator                                             | Implicit | One byte | DAA   |

|        |                                                                        |          |          |       |

## Figure 1.8: Arithmetic Instructions of 8085

### Logical instruction

These instructions perform logical operation with content of accumulator. These instructions are AND, OR, Ex-OR, rotate, compare, and complement.

### Logical AND

Any 8-bit number, or the content of a register, or the content of a memory location can be logically ANDed with the content of accumulator. The result is stored in the accumulator.

| Mnemonics | Tasks performed on execution                                    | Addressing<br>mode | Length of<br>the<br>Instruction | Example |

|-----------|-----------------------------------------------------------------|--------------------|---------------------------------|---------|

| ANI 8-bit | Logical AND immediate with accumulator                          | Immediate          | Two bytes                       | ANI OFH |

| XRI 8-bit | Exclusive OR immediate with accumulator                         | Immediate          | Two bytes                       | XRI 01H |

| ORI 8-bit | Logical OR immediate with accumulator                           | Immediate          | Two bytes                       | ORI 80H |

| ANA R     | Logical AND register or memory with accumulator                 | Direct             | One byte                        | ANA C   |

| XRA R     | Exclusive OR register or memory with accumulator                | Direct             | One byte                        | XRA D   |

| ORA R     | Logical OR register or memory with accumulator                  | Direct             | One byte                        | ORA E   |

| ANA M     | Logical AND memory pointed by HL register pair with accumulator | Indirect           | One byte                        | ANA M   |

| XRA M     | Logical XOR memory pointed by HL register pair with accumulator | Indirect           | One byte                        | XRA M   |

| ORA M     | Logical OR memory pointed by HL register pair with accumulator  | Indirect           | One byte                        | ORA M   |

| RLC       | Rotate accumulator left                                         | Implicit           | One byte                        | RLC     |

| RRC       | Rotate accumulator right                                        | Implicit           | One byte                        | RRC     |

| RAL       | Rotate accumulator left through carry                           | Implicit           | One byte                        | RAL     |

| RAR       | Rotate accumulator right through carry                          | Implicit           | One byte                        | RAR     |

| CPI 8-bit | Compare immediate with accumulator                              | Immediate          | Two bytes                       | CPI FFH |

| CMP R     | Compare register or memory with accumulator                     | Direct             | One byte                        | CMP B   |

| СМР М     | Compare memory pointed by HL register pair with accumulator     | Indirect           | One byte                        | CMP M   |

| СМА       | Complement accumulator                                          | Implicit           | One byte                        | CMA     |

| СМС       | Complement carry                                                | Implicit           | One byte                        | CMC     |

| STC       | Set carry                                                       | Implicit           | One byte                        | STC     |

Figure 1.9: Logical Instructions of 8085

### **Branching Instructions**

This instruction alters the sequence of program execution either conditionally or unconditionally. These instructions are jump, call, return, and restart.

| Mnemonics   | Tasks performed on execution | Addressing mode | Length of the<br>Instruction | Example      |

|-------------|------------------------------|-----------------|------------------------------|--------------|

| JMP 16-bit  | Jump unconditionally         | Immediate       | Three bytes                  | JMP<br>9500  |

| JC 16-bit   | Jump if carry is set         | Immediate       | Three bytes                  | JC 9500      |

| JNC 16-bit  | Jump on no carry             | Immediate       | Three bytes                  | JNC<br>9500  |

| JP 16-bit   | Jump on positive             | Immediate       | Three bytes                  | JP 9500      |

| JM 16-bit   | Jump on minus                | Immediate       | Three bytes                  | JM 9500      |

| JZ 16-bit   | Jump on zero                 | Immediate       | Three bytes                  | JZ 9500      |

| JNZ16-bit   | Jump on no zero              | Immediate       | Three bytes                  | JNZ<br>9500  |

| JPE 16-bit  | Jump on parity even          | Immediate       | Three bytes                  | JPE<br>9500  |

| JPO 16-bit  | Jump on parity odd           | Immediate       | Three bytes                  | JPO<br>9500  |

| CALL 16-bit | Call unconditionally         | Immediate       | Three bytes                  | CALL<br>9500 |

| CC 16-bit   | Call on carry                | Immediate       | Three bytes                  | CC 9500      |

| CNC 16-bit  | Call on no carry             | Immediate       | Three bytes                  | CNC<br>9500  |

| CP 16-bit   | Call on positive             | Immediate       | Three bytes                  | CP 9500      |

| CM 16-bit   | Call on minus                | Immediate       | Three bytes                  | CM<br>9500   |

| CZ 16-bit   | Call on zero                 | Immediate       | Three bytes                  | CZ 9500      |

| CNZ 16-bit  | Call on no zero              | Immediate       | Three bytes                  | CNZ<br>9500  |

| CPE 16-bit  | Call on parity even          | Immediate       | Three bytes                  | CPE<br>9500  |

| CPO 16-bit  | Call on parity odd           | Immediate       | Three bytes                  | CPO<br>9500  |

| RET         | Return unconditionally       | Implicit        | One byte                     | RET          |

| RC          | Return on carry              | Implicit        | One byte                     | RC           |

| RNC         | Return on no carry           | Implicit        | One byte                     | RNC          |

| RP          | Return on positive           | Implicit        | One byte                     | RP           |

| RM                     | Return on minus                 | Implicit | One byte | RM    |

|------------------------|---------------------------------|----------|----------|-------|

| RZ                     | Return on zero                  | Implicit | One byte | RZ    |

| RNZ                    | Return on no zero               | Implicit | One byte | RNZ   |

| RPE                    | Return on parity even           | Implicit | One byte | RPE   |

| RPO                    | Return on parity odd            | Implicit | One byte | RPO   |

| PCHL                   | Copy HL contents to the program | Implicit | One byte | PCHL  |

| RST<br>0/1/2/3/4/5/6/7 | Restart                         | Implicit | One byte | RST 5 |

# Figure 1.10: Branch Instructions of 8085

# Machine control operation

These instruction are halt, interrupt, and do nothing etc.

| Mnemonics | Tasks performed on execution      | Addressing mode | Length of the<br>Instruction |

|-----------|-----------------------------------|-----------------|------------------------------|

| NOP       | No operation                      | Implicit        | One byte                     |

| HLT       | Halt the microprocessor execution | Implicit        | One byte                     |

| DI        | Disable interrupts                | Implicit        | One byte                     |

| EI        | Enable interrupts                 | Implicit        | One byte                     |

| RIM       | Read interrupt mask               | Implicit        | One byte                     |

| SIM       | Set interrupt mask                | Implicit        | One byte                     |

Figure 1.11: Machine Instructions of 8085

Assembly Language Programming using 8085 instruction set

Statement: Add the content of memory location 4000H with content of memory location 4001H and place the result in memory location 4002H.

(4000H) = 14H (4001H) = 89H Result = 14H + 89H = 9DH Source program LXI H 4000H : HL points 4000H MOV A, M : Get first operand INX H : HL points 4001H ADD M : Add second operand INX H : HL points 4002H MOV M, A : Store result at 4002H HLT : Terminate program execution

Statement: Subtract the contents of memory location 4001H from the memory location 2000H and place the result in memory location 4002H.

Program - 4: Subtract two 8-bit numbers

Sample problem:

(4000H) = 51H

(4001H) = 19H

Result = 51H - 19H = 38H

LXI H, 4000H : HL points 4000H

MOV A, M : Get first operand

INX H : HL points 4001H

SUB M : Subtract second operand

INX H : HL points 4002H

MOV M, A : Store result at 4002H.

HLT : Terminate program execution

#### **MODULE-2**

#### **Memory interfacing**

#### Introduction: RAM, ROM, EPROM

The programs and data which are executed by the microprocessor have to be stored in ROM/EPROM and RAM which are basically semiconductor memory chips.

The programs and data which are stored in ROM/EPROM are not erased even-though the power supply to the ROM/EPROM chip is removed. Hence the ROM/EPROM are called non-volatile memory and we can use them to store permanent programs such as monitor program and data such as look up table, which are needed in microprocessor based systems. The difference between ROM and EPROM is that ROM chip is programmable only one time whereas an EPROM chip can be programmed many times.

The programs and data which are stored in RAM are erased when the power supply to the RAM chip is removed and hence RAM is called volatile memory. The program written during the learning of assembly language programming and data entered while testing the above programs are stored in RAM.

#### Interfacing memory chips with 8085

8085 has 16 address lines namely (A15 to A0), a maximum of 64Kbytes ( $=2^{16}$ ) memory can be interfaced with 8085. The 64 KB memory address space of 8085 has the value from 0000H to FFFFH when represented in hexadecimal form.

The 8085 access memory to read the instructions and data stored in memory and also to store the result in to memory.

The 8085 initiates a set of signals and when it wants to read from and write into memory and the memory chip has certain signals such as chip Enable or Chip Select, or Output Enable or Read and or Write Enable or Write.

| IO/M | RD | WR | Operation                                       |

|------|----|----|-------------------------------------------------|

| 0    | 0  | 1  | The 8085 reads data from memory (RAM or EPROM). |

| 0    | 1  | 0  | The 8085 writes data into memory (RAM).         |

### Figure 2.1: Generation of control signal for memory

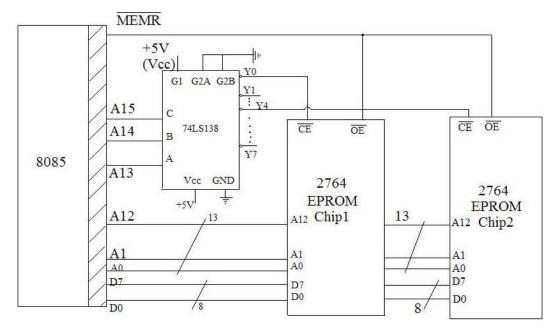

#### Interfacing 2764 EPROM chip with 8085

There are 13 address lines (Since  $2^{13}$  =8K) namely A12 to A0 present in IC 2764 (Fig. 2.1) where A0 is the least significant bit of the address and A12 is the most significant bit of the address.

In order to read the content of a memory location in EPROM chip, the following steps are done

- The address of the memory location from where data has to be read is placed in the address lines of EPROM.

- CE signal is made logic low (i.e. 0)

- OE signal is made logic low(i.e. 0)

- Now the data in the selected memory location will be available in the data lines (D7-D0) of EPROM.

| Vpp  | ) —                  | 1  |       | 28  | — Vcc |

|------|----------------------|----|-------|-----|-------|

| A12  | 2 —                  | 2  |       | 27  | — P   |

| A7   | 3 <u>-</u> 2         | 3  |       | 26  | -NC   |

| A6   | ( <del>) (</del>     | 4  |       | 25  | — A8  |

| A5   | 3 <del>1 - 5</del>   | 5  |       | 24  | — A9  |

| A4   | 3 <u>0 - 2</u>       | 6  | 2764  | 23  | — A11 |

| A3   | <del>22 - 54</del>   | 7  | 8KX8  | 22  | —OE   |

| A2   | (9                   | 8  | EPROM | I21 | — A10 |

| A1   | 9 <del>97 - 20</del> | 9  |       | 20  | -CE   |

| A0   | 3 <del>3 - 3</del>   | 10 |       | 19  | —D7   |

| D0   | <u>10 8</u>          | 11 |       | 18  | — D6  |

| D1   |                      | 12 |       | 17  | — D5  |

| D2   | <del>15 - 52</del>   | 13 |       | 16  | — D4  |

| Vss  | ( <u>2</u>           | 14 |       | 15  | — D3  |

| (Gno | 1)                   |    |       | 5   |       |

Figure 2.2: Pin diagram of IC 2764

Whenever many number of same capacity memory chips have to be interfaced with 8085, decoder IC with active low outputs such as 74LS138 is very useful.

By using a single 74LS138 IC, maximum of eight memory chips (RAM and EPROM) can be interfaced with 8085.

### Partial address decoding:

If the entire address bus of 8085 (A15 to A0) is used to interface memory chips with 8085 than this technique is called absolute address decoding. Using the absolute address decoding method, maximum of 64 Kbytes of memory can be interfaced with 8085.

There is another method known as partial address decoding which is used when the amount of memory needed in an 8085 based system is less than 64 Kbytes such as 8K or 16K or 32K.

Figure 2.3: Interfacing EPROM chips using 74LS138 Decoder

## Interfacing 6264 RAM chip with 8085

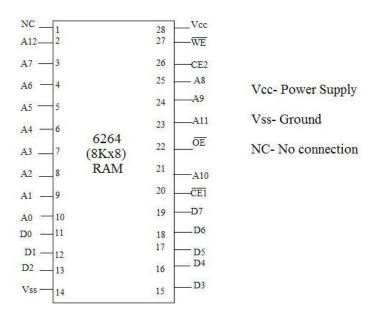

The interfacing of RAM chip with 8085 is same as that of EPROM chip except that one more signals namely write of 8085 is used.6264 RAM has 13 address lines.

Figure 2.4: Pin diagram of IC 6264 RAM

### **Stack and Subroutines**

The stack is an area of R/W memory identified by the programmer for temporary storage of information.

- The stack is a Last in First out (LIFO) structure.

- The stack normally grows backwards into memory.

In other words, the programmer defines the bottom of the stack and the stack grows up into reducing address range.

Given that the stack grows backwards into memory, it is customary to place the bottom of the stack at the end of memory to keep it as far away from user programs as possible.

In the 8085, the stack is defined by setting the SP (Stack Pointer) register.

LXI SP, FFFFH

This sets the Stack Pointer to location FFFFH (end of memory for the 8085).

The Size of the stack is limited only by the available memory

### Saving Information on the Stack

Information is saved on the stack by PUSH ing it on. It is retrieved from the stack by POPing it off.

The 8085 provides two instructions: PUSH and POP for storing information on the stack and retrieving it back. Both PUSH and POP work with register pairs only.

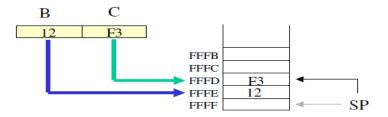

The PUSH Instruction

PUSH B (1 Byte Instruction).

Decrement SP, Copy the contents of register B to the memory location pointed to by SP.

Decrement SP, Copy the contents of register C to the memory location pointed to by SP

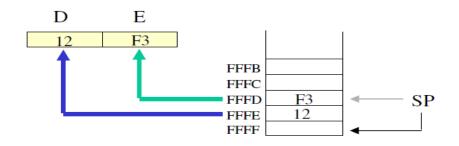

The POP Instruction

POP D (1 Byte Instruction).

Copy the contents of the memory location pointed to by the SP to register E, Increment SP.

Copy the contents of the memory location pointed to by the SP to register D, Increment SP.

### **Operation of the Stack**

During pushing, the stack operates in a "decrement then store" style.

The stack pointer is decremented first, and then the information is placed on the stack.

During popping, the stack operates in a "use then increment" style.

The information is retrieved from the top of the, the stack and then the pointer is incremented.

The SP pointer always points to "the top of the stack".

### LIFO

The order of PUSHs and POPs must be opposite of each other in order to retrieve information back into its original location.

PUSH B

PUSH D

...

POP D

POP B

Reversing the order of the POP instructions will result in the exchange of the contents of BC and DE.

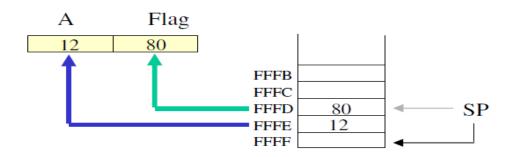

### The PSW Register Pair

The 8085 recognizes one additional register pair called the PSW (Program Status Word).

This register pair is made up of the Accumulator and the Flags register.

It is possible to push the PSW onto the stack, do whatever operations are needed, then POP it off of the stack.

The result is that the contents of the Accumulator and the status of the Flags are returned to what they were before the operations were executed.

### **PUSH PSW Register Pair**

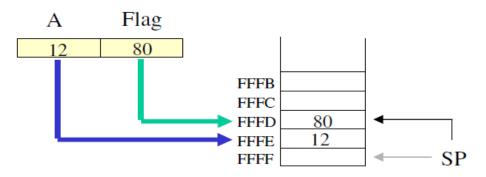

PUSH PSW (1 Byte Instruction).

Decrement SP, Copy the contents of register A to the memory location pointed to by SP. Decrement SP, Copy the contents of Flag register to the memory location pointed to by SP.

### **Pop PSW Register Pair**

POP PSW (1 Byte Instruction).

Increment SP, Copy the contents of the memory location pointed to by the SP to Flag register Increment SP, Copy the contents of the memory location pointed to by the SP to register A

## Subroutines

A subroutine is a group of instructions that will be used repeatedly in different locations of the program.

Rather than repeat the same instructions several times, they can be grouped into a subroutine that is called from the different locations.

In Assembly language, a subroutine can exist anywhere in the code. However, it is customary to place subroutines separately from the main program.

The 8085 has two instructions for dealing with subroutines.

The CALL instruction is used to redirect program execution to the subroutine.

The RET instruction is used to return the execution to the calling routine.

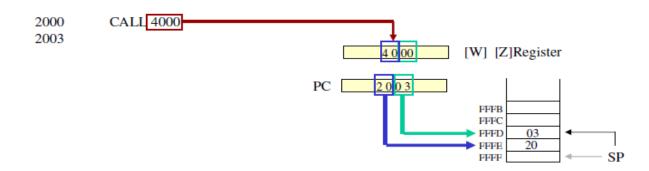

## CALL 4000H (3 byte instruction)

When CALL instruction is fetched, the Processor knows that the next two memory location contains 16bit subroutine address in the memory.

The Processor Reads the subroutine address from the next two memory location and stores the higher order 8-bit of the address in the W register and stores the lower order 8-bit of the address in the Z register

Push the address of the instruction immediately following the CALL onto the stack.

Loads the program counter with the 16-bit address supplied with the CALL instruction from WZ register.

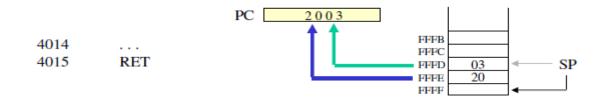

### **RET (1 byte instruction)**

Retrieve the return address from the top of the stack

Load the program counter with the return address.

Subroutine provides flexibility in writing program and uses memory efficiently.

### Nesting:

The programming technique of a subroutine calling another subroutine is called nesting of subroutine. This process is limited only by available stack locations.

### **Recursive Subroutine:**

A subroutine which is called by itself is called recursive subroutine.

### **Reentrant Subroutine:**

In nested subroutine, if a latter subroutine calls an earlier subroutine, it is known as reentrant subroutine.

### **Multiple Ending Subroutines:**

The subroutine which has more than one return is called multiple ending subroutines.

### Multiple Calling of subroutine:

Calling a subroutine more than once by main program are called multiple calling subroutines.

### Parameter passing:

It is necessary pass data and address variable of main program to subroutine. This passing of data and address is called parameter passing. Parameter passing can be done by using register, pointer, memory and stack.

### 8085 Interrupts

### Introduction

Interrupts are mainly used for interrupt driven data transfer between processor and slower input/ output device. The primary function of the microprocessor is to accept data from input devices such as keyboards and A/D converters, read instruction from memory, process data according to the instructions, and send the results to output device such as LEDs, printers and video monitors. The 8085 has five number of interrupt pins: TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR.

When the 8085 is interrupted by external devices, it is called hardware interrupt. In software interrupt, the program execution is interrupted by using software instruction.

## **Types of Interrupts**

- Vectored and Non-vectored Interrupts

- Maskable and Non-maskable Interrupts

- Software and Hardware Interrupt

### Interrupt Handling Procedure

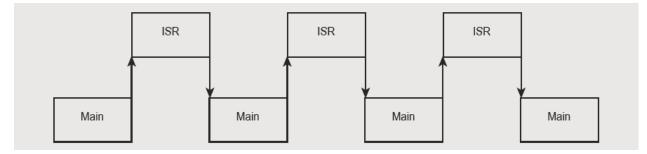

The Processor will have to store the information about the current program when an interrupt signal is recognized before executing the ISR. The processor checks for the Interrupt request signals at the end of every instruction execution. If the interrupt is masked, then the interrupt will not be recognized until interrupts are re-enabled. The sequence of operations that take place when an interrupt signal is recognized is as followed. The CPU responds to an interrupt request by a transfer of control to another program in a manner similar to a subroutine call. Save the PC (Program Counter) contents (address of the next instruction) and supplementary information about current state (flags, registers, etc.) to the stack. Load PC with the beginning address of an Interrupt Service Routine (ISR) and start to execute it. Finish ISR when return instruction is executed. Return to the interrupted program, exactly to the same point from which it left.

Figure 2.5: Transfer of control from Main memory to ISR

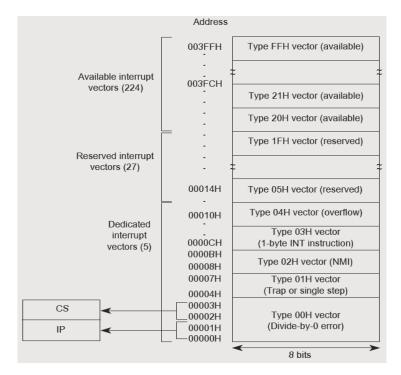

### Interrupt Sources and their Vector Addresses in 8085

Intel 8085 has the facility for both software and hardware interrupts. The software interrupts are in the form of instructions and the hardware interrupts are applied as signals from the external devices.

### **Hardware Interrupts and Priorities**

Intel 8085 has 5 hardware interrupts: INTR, RT 5.5, RST 6.6, RST 7.5, and TRAP. The details of the five interrupts are given in the table 2.1. Five pins of 8085 are reserved for the five hardware interrupts. All the five interrupts are active high signals. This means that in order to apply an interrupt, logic 1 or high level signal should be applied at these pins. The processor checks the voltage on these pins after the execution of every instruction. If the signal level on any of these 5 pins is at logic 1 and the corresponding interrupt is not masked, then the processor will suspend the current program and execute the corresponding interrupt service routine. RST 7.5 interrupt alone is edge triggered. That means a logic 0 to 1 transition will be treated as an interrupt input on this line. The rising edge interrupt can be applied at any time and this will set a flip flop inside the processor. The processor will check this flip flop while checking the signal level on other hardware interrupts.

| Interrupt | Interrupt vector<br>address | Maskable or Non<br>Maskable | Edge-or Level-<br>triggered | priority |

|-----------|-----------------------------|-----------------------------|-----------------------------|----------|

| Trap      | 0024H                       | Non-maskable                | Level-triggered             | 1        |

| RST 7.5   | 003CH                       | Maskable                    | Rising edge<br>triggered    | 2        |

| RST 6.5   | 0034H                       | Maskable                    | Level-triggered             | 3        |

| RST 5.5   | 002CH                       | Maskable                    | Level-triggered             | 4        |

| INTR      | Decided by<br>Hardware      | Maskable                    | Level-triggered             | 5        |

## Table 2.1: Hardware interrupts in 8085

### Software Interrupts

8085 microprocessor instruction set has eight software interrupts instruction called Restart (RST) instructions. These are one-byte call instruction that transfer program execution to subroutine at predefined address. Table2.2 gives the eight software instructions and their corresponding interrupt vector address.

The vector address for a software interrupt is calculated as follows:

Vector address = interrupt number x 8.

The vector address for RST 5 is calculated as

$5x 8=40_{10}=28H$ . So vector address of RST 5 is 0028H

| Instruction | Machine hex Code | Interrupt Vector<br>address |

|-------------|------------------|-----------------------------|

| RST 0       | C7               | 0000H                       |

| RST 1       | CF               | 0008H                       |

| RST 2       | D7               | 0010H                       |

| RST 3       | DF               | 0018H                       |

| RST 4       | E7               | 0020H                       |

| RST 5       | EF               | 0028H                       |

| RST 6       | F7               | 0030H                       |

| RST 7       | FF               | 0038H                       |

Table 2.2: Software interrupts and their Vector address

#### **Masking of Interrupts**

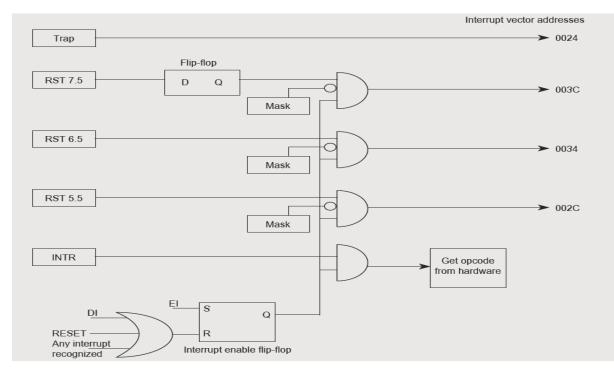

The 8085 interrupt structure is shown in figure 2.5. The maskable interrupts are by default masked by the RESET signal. So, any interrupt will not be recognized by the hardware reset. The interrupts can be enabled by the execution of the instruction, EI – Enable interrupts. The three RST interrupts can be selectively masked by having proper word in Accumulator and executing the SIM (Set Interrupt Mask) instruction. This is called software masking. All the maskable interrupts are disabled whenever an interrupt is recognized. So, it is necessary to execute EI instruction every time the interrupts are recognized and serviced by the processor. All the maskable interrupts can be disabled by executing an instruction DI – Disable Interrupts. This instruction will reset an interrupt enable flip flop in the processor and the interrupts will be disabled. To enable interrupts, EI instruction has to be executed.

Figure 2.6: interrupts structure of 8085

#### **SIM Instruction**

The SIM instruction is used to mask or unmask the restart RST hardware interrupts. Figure 2.7 shows the SIM instruction format. The SIM instruction when executed will read the contents of the accumulator and based on that will mask or unmask the interrupts. So, SIM instruction must be executed after storing having proper control word in accumulator. The format of the control word is to be stored in accumulator before executing SIM instruction.

| Bit position | D7                              | D6                                                      | D5          | D4                            | D3                                                       | D2                                   | D1                                   | D0                                   |

|--------------|---------------------------------|---------------------------------------------------------|-------------|-------------------------------|----------------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| Name         | SOD                             | SDE                                                     | Х           | R7.5                          | MSE                                                      | <b>M</b> 7.5                         | M6.5                                 | <b>M</b> 5.5                         |

| Explanation  | Serial<br>data<br>to be<br>sent | Serial<br>data<br>enable—<br>set to<br>1 for<br>sending | Not<br>used | Reset<br>RST 7.5<br>flip-flop | Mask set<br>enable—<br>Set to 1<br>to mask<br>interrupts | Set to<br>1 to<br>mask<br>RST<br>7.5 | Set to<br>1 to<br>mask<br>RST<br>6.5 | Set to<br>1 to<br>mask<br>RST<br>5.5 |

Figure 2.7: SIM instruction Format

The instructions required for execution of SIM are

MVI A, control word

SIM

### **RIM Instruction**

RIM stands for 'Read Interrupt Mask' and its format is shown in figure 2.8. When RIM instruction is executed, the status of serial input data (SID), pending interrupts and interrupt masks are loaded into accumulator.

| Bit<br>position | D7            | D6               | D5               | D4               | D3                                             | D2               | D1                                     | D0               |

|-----------------|---------------|------------------|------------------|------------------|------------------------------------------------|------------------|----------------------------------------|------------------|

| Name            | SID           | I7.5             | I6.5             | I5.5             | IE                                             | <b>M</b> 7.5     | M6.5                                   | <b>M</b> 5.5     |

| Explanation     | input<br>data | if RST<br>7.5 is | if RST<br>6.5 is | if RST<br>5.5 is | Set to<br>1 if<br>interrupts<br>are<br>enabled | if RST<br>7.5 is | Set to 1<br>if RST<br>6.5 is<br>masked | if RST<br>5.5 is |

Figure 2.8: RIM instruction Format

The instructions required for execution of RIM are

MVI A, control word

RIM

### **MODULE-3**

#### **PROGRAMMABLE PERIPHERAL INTERFACE: 8255**

#### Introduction

Intel 8085 microprocessor can transfer data between external devices such as input devices and output devices through ports. Normally a register can act as an I/O port. But having a separate register and configuring them for input and output operation becomes difficult and tedious. So, Intel has designed a separate IC 8255 with the objective of interfacing input and output devices with Intel microprocessors. The 8255 Programmable Peripheral Interface (PPI) is a very popular and versatile input / output chip that can be easily programmed to function in several different configurations. The common application of 8255 with 8085 include turning on a switch, to control movement by use of motors, to detect position etc.

### Features of 8255

Each 8255 has three 8-bit TTL- compatible registers or ports which will allow the programmers to control digital outputs of up to 24 bits or to read 24 bit inputs, or control a combination of both input and output.

The common features of Intel 8255 IC are as followed.

- Three 8-bit ports named as Port A, Port B, Port C.

- Port C has been divided to two groups of 4 bits each as Port C upper (PCU) and Port C lower (PCL).

- It can operate in mode 0, mode1, mode2, and BSR (bit set reset) mode.

- The port can be programmed for simple I/O or Handshake I/O or bidirectional data bus for the data transfer in I/O modes.

- Each Port C bit can be set/reset individually in BSR mode.

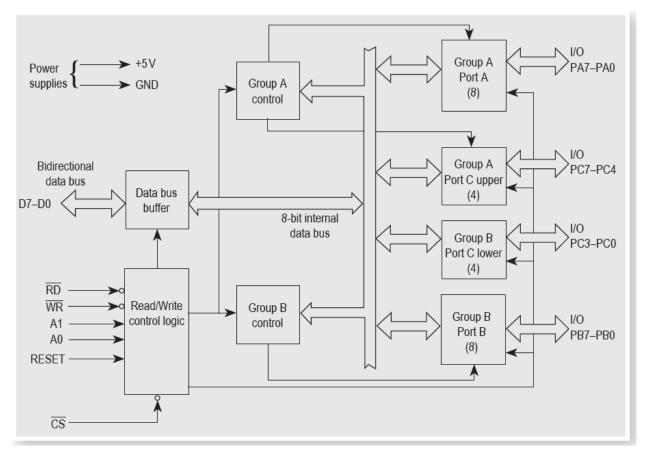

### Block Diagram of INTEL 8255

The block diagram of 8255 PPI is shown in figure 3.1. The block diagram consist of Port A, Port C upper Port B, Port C lower, data bus buffer, read write control logic.

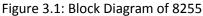

Pin Diagram of 8255

### Description of Block diagram

- The block diagram of 8255 (Fig.3.1) has three basic registers of 8 bits each and are called as Port A, Port B and Port C.

- The port A and upper 4 bits of Port C are grouped and called as Group A.

- Similarly, Port B and lower 4 bits of Port C are grouped as Group B.

- The data bus buffer (D7-D0).

- In addition to three Ports, there is another register called control register.

- The contents written into the control register decides the operating modes of the three parallel ports.

- In order to identify Ports and control word register, 8255 uses two address lines A0 and A1.

The selection of the ports and control register (Table 3.1) are based on chip select (CS) signal and A0 and A1 is

| Chip   | A1 | A0 | Selection             |

|--------|----|----|-----------------------|

| Select |    |    |                       |

| 0      | 0  | 0  | Port A                |

| 0      | 0  | 1  | Port B                |

| 0      | 1  | 0  | Port C                |

| 0      | 1  | 1  | Control Word Register |

Table 3.1: Port and Control Word Register selection

## **Control Logic**

- RD (Read): When RD signal is low, processor reads data from selected I/O port of 8255.

- WR (write): When WR signal is low, processor writes into a selected I/O port or control register of 8255..

- Reset: when reset is high, it clears control register and sets all ports in the input mode.

- CS, A1 and A0: Chip Select (CS) is connected to decoded address.A1 and A0 of 8255 are connected to A1 and A0 of processor.

To communicate with peripherals through 8255, the following steps are necessary:

- Determine address of Port-A, Port-B, Port-C and control word register.

- Write a control word in control word register.

- Write input and output instruction.

### **Description of various Modes of 8255**

### I/O Mode:

Input/output mode is selected when bit D7=1 of the control word register.

### Mode 0: Simple input or output for Port A, Port B, and Port C.

- Outputs are latched.

- Inputs are not latched.

- Ports do not have handshake or interrupt capability.

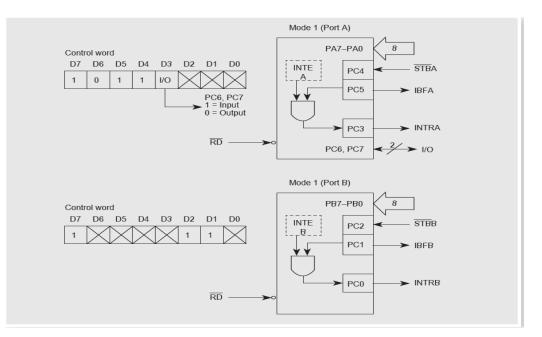

Mode 1: Handshake I/O for Port A, Port B. Port-C bits is used as handshake signal.

- Inputs are latched.

- Handshake and interrupt capability.

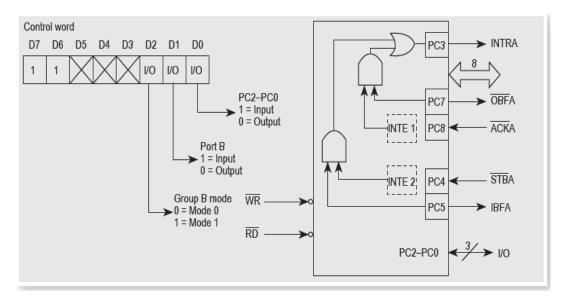

Mode 2: Bi-directional Bus for Port A. Port-C bits is used as handshake signal.

| D7                | D6 D5                                                         | D4                | D3                                                         | D2                                                | D1 | D0                                                            |

|-------------------|---------------------------------------------------------------|-------------------|------------------------------------------------------------|---------------------------------------------------|----|---------------------------------------------------------------|

| 1<br>(1 =<br>I/O) | Group A<br>Mode select<br>00—mode 0<br>01—mode 1<br>1X—mode 2 | select<br>1—input | Port C upper<br>Direction<br>select<br>1—input<br>0—output | Group B<br>Mode<br>select<br>0—mode 0<br>1—mode 1 |    | Port C<br>lower<br>Direction<br>select<br>1—input<br>0—output |

Figure 3.2: I/O Control Word Format

# BSR Mode:

BSR means bit set reset mode for Port C.BSR mode mode is selected when bit D7=0 of the control word register.

| D7        | D6                   | D5     | D4     | D3 | D2                  | D1 | DO                                    |

|-----------|----------------------|--------|--------|----|---------------------|----|---------------------------------------|

| (0 = BSR) | X<br>(Don't<br>care) | (Don't | (Don't |    | B1<br>bits—select o |    | Bit set/reset<br>1 = set<br>0 = reset |

Figure 3.3: BSR mode Control Word Format

- In BSR mode, any of the eight bits of Port C can be Set or Reset.

- It is used for control or on/off switch.

- BSR mode does not affect I/O mode.

Figure 3.4: Mode1: Input Configuration

The operation of handshake signals for the input operation in 8255 is explained with the figure 3.4. The sequence of operations for the data input operation from an input device to microprocessor through 8255 is listed as follows.

- STB (Strobe Input): The input device places data in the data lines i.e., the Port A or Port B lines. This is communicated to 8255 by making STB low. STB is an active low signal applied to PC4 or PC2.

- IBF (Input Buffer Full): 8255 acknowledges the receipt of the data to the input by making IBF high. This also indicates that the data has been latched into the input port.

- INTR (Interrupt Request): 8255 then makes INTR output line high and applies an interrupt to the processor. INTR signal is generated only if STB, IBF, and INTE are all high at the same time.

- INTE (Interrupt Enable): INTE is an internal flip flop. INTE for Port A is controlled by bit set/reset of PC4 and INTE for port B is controlled by bit set/reset of PC2. PC2 and PC4 can be controlled using BSR mode.

- RD (Read): The processor in the interrupt service routine reads the data from the corresponding input port. Reading from the port is done by selecting the 8255 port and applying RD active low signal. When RD signal goes low, INTR signal is reset. IBF is reset by the rising edge of the RD input.

The entire procedure explained above for mode1 allows an input device to request service from the CPU by simply sending its data into the port and giving STB signal.

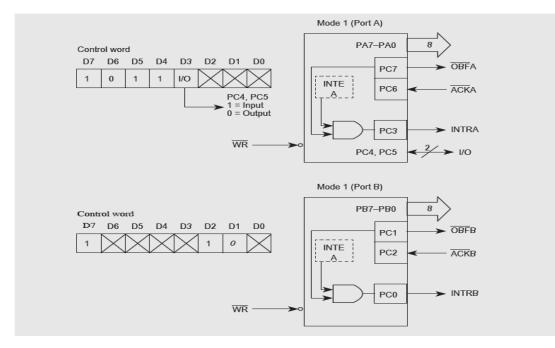

#### Mode1: OUTPUT CONTROL SIGNALS

Figure 3.5: 8255 Mode1: Output Configuration

The control signals when Port A and Port B are configured as output ports in mode1 are shown in figure 3.5.

- WR (Write): The processor will initiate the data transmission by writing the data to be transmitted to the output device to the corresponding port of 8255. This is done by processor by sending the port address to 8255 and data on the data lines and then giving the active low WR signal.

- OBF (Output Buffer Full): This is an output signal that goes low when CPU writes data into the output latch of 8255. This signal indicates to an output peripherals that new data is ready to be read. It goes high again after the 8255 receives an acknowledge from peripherals.

- ACK (Acknowledge): This is an input signal from peripheral that goes low when peripheral receives data from 8255 ports.

- INTR (Interrupt Request): This is an output signal. This can be used to interrupt CPU to request the next data byte for output. The INTR is set when OBF.ACK and INTE are all one and reset by falling edge of WR.

- INTE (Interrupt Enable): This is an internal flip flop and set one to generate the INTR signal. INTE<sub>A</sub> and INTE<sub>B</sub> are controlled by bits PC<sub>6</sub> and PC<sub>2</sub>respectively through BSR mode.

### Mode 2 : Bidirectional Data Transfer

Figure 3.6: 8255 Mode 2: Bidirectional Input/output

Figure 3.6 shows mode2 bidirectional input/output port for Port A. This mode is used primarily in data transfer between two computers. Port A is configured as bidirectional port. Port A uses five signals from Port C as handshake signal for data transfer. The input and output operation of 8255 in mode2 is similar to the operation in mode 1 except that the Port A is bidirectional port. The data is transmitted and received through the Port A lines.

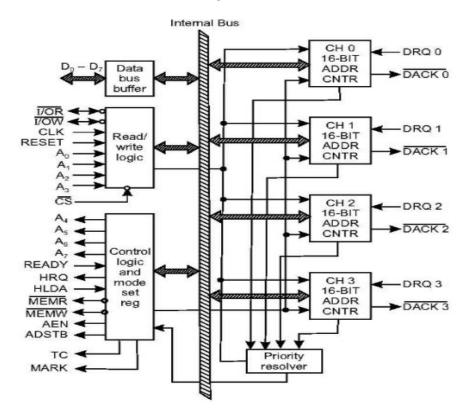

### PROGRAMMABLE DMA CONTROLLER 8257

### Introduction

8257 is Intel direct memory access controller (DMA) IC. Peripheral devices access memory directly by passing processor. So it is faster method of memory access over programmed data transfer for memory access. The features of 8257 are as follows:

- It is a four channel DMA controller IC.

- A maximum 16 KB data transfer can be done sequentially at a time.

- 8257 is initialized for each channel by starting address, number of bytes of data to be transferred, mode of operation.

- It executes 3 DMA cycles: DMA read, DMA write, DMA verify.

- It generates a TC signal to indicate the peripheral that the programmed numbers of data bytes have been transferred.

- It generates MARK signal to indicate the peripheral that 128 bytes have been transferred.

- It provide AEN signal that can be used to isolate CPU and other devices from the system bus.

- It operates in two modes: Master Mode, Slave Mode.

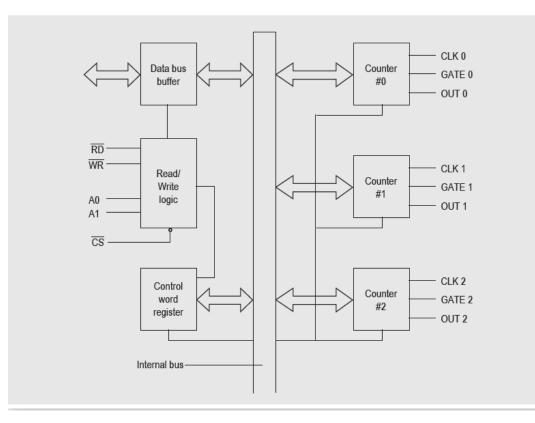

Figure 3.7 shows block diagram of 8257 DMA controller. The internal block diagram of 8257 consists of eight blocks: data bus buffer, read/write block, control logic and mode set register, priority resolver and four channel blocks.

Pin Diagram of 8257

Figure 3.7: Block Diagram of 8257

• Each channel of 8257 Block diagram has two programmable 16-bit registers named as address register and count register.

- Address register is used to store the starting address of memory location for DMA data transfer.

- The address in the address register is automatically incremented after every read/write/verify transfer.

- The count register is used to count the number of byte or word transferred by DMA. The format of count register is shown in figure 3.8.

| D15          | D14          | D13       | D12     | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--------------|--------------|-----------|---------|-----|-----|----|----|----|----|----|----|----|----|----|----|

| $\downarrow$ | $\downarrow$ |           |         |     |     |    |    |    |    |    |    |    |    |    |    |

| 0 0          | 1            | /erify ti | ransfer | r   |     |    |    |    |    |    |    |    |    |    |    |

| 0 1          | \            | Vrite tr  | ransfer | •   |     |    |    |    |    |    |    |    |    |    |    |

| 10           | F            | Read tra  | ansfer  |     |     |    |    |    |    |    |    |    |    |    |    |

| 1 1          | 1            | llegal    |         |     |     |    |    |    |    |    |    |    |    |    |    |

Figure 3.8: Count Register Format

- 14-bits B0-B13 is used to count value and a 2-bits is used for indicate the type of DMA transfer (Read/Write/Veri1 transfer).

- In read transfer the data is transferred from memory to I/O device.

- In write transfer the data is transferred from I/O device to memory.

- Verification operations generate the DMA addresses without generating the DMA memory and I/O control signals.

The 8257 has two eight bit registers called mode set register and status register. The format of mode set register is shown in figure 3.9.

| B7        | B6 | B5 | B4 | B3   | B2   | B1   | BO   |

|-----------|----|----|----|------|------|------|------|

| Auto-load | ТС | EW | RP | CH-3 | CH-2 | CH-1 | CH-0 |

Figure 3.9: Mode Set Register Format

The use of mode set register is

- Enable/disable a channel.

- Fixed/rotating priority

- Stop DMA on terminal count.

- Extended/normal writes time.

- Auto reloading of channel-2.

- The bits B0, B1, B2, and B3 of mode set register are used to enable/disable channel -0, 1, 2 and 3 respectively. A one in these bit position will enable a particular channel and a zero will disable it.

- If the bit B4 is set to one, then the channels will have rotating priority and if it zero then the channels wilt have fixed priority.

1. In rotating priority after servicing a channel its priority is made as lowest.

2. In fixed priority the channel-0 has highest priority and channel-2 has lowest priority.

- If the bit B5 is set to one, then the timing of low write signals (MEMW and IOW) will be extended.

- If the bit B6 is set to one then the DMA operation is stopped at the terminal count.

- The bit B7 is used to select the auto load feature for DMA channel-2.

- When bit B7 is set to one, then the content of channel-3 count and address registers are loaded in channel-2 count and address registers respectively whenever the channel-2 reaches terminal count. When this mode is activated the number of channels available for DMA reduces from four to three.

Figure 3.10 shows the eight bit status register format of 8257. It is used to read the status of terminal count of the four channels (CH0-CH3).

| B7 | B6 | B5 | B4 | B3   | B2   | B1   | BO   |

|----|----|----|----|------|------|------|------|

| 0  | 0  | 0  | UF | CH-3 | CH-2 | CH-1 | CH-0 |

### Figure 3.10: Status Register Format

- The bit B0, B1, B2, and B3 of status register indicates the terminal count status of channel-0, 1,2 and 3 respectively. A one in these bit positions indicates that the particular channel has reached terminal count.

- These status bits are cleared after a read operation by microprocessor.

- The bit B4 of status register is called update flag and a one in this bit position indicates that the channel-2 register has been reloaded from channel-3 registers in the auto load mode of operation.

### PROGRAMMABLE INTERRUPT CONTROLLER: 8259

### Introduction

The Intel 8259 is a Programmable Interrupt Controller (PIC) designed for use with the 8085 and 8086 microprocessors. The 8085 has only five number of hardware interrupts: TRAP,RST 7.5.RST 6.5,RST 5.5 and INTR. The 8259 can be used for applications that use more than five numbers of interrupts from multiple sources.

### Features and Architecture of 8259

The main features of 8259 are listed below.

- Manage eight levels of interrupts.

- Eight interrupts are spaced at the interval of four or eight locations.

- Resolve eight levels of priority in fully nested mode, automatic rotation mode or specific rotation mode.

- Mask each interrupt individually.

- Read the status of pending interrupt, in-service interrupt, and masked interrupt.

- Accept either the level triggered or edge triggered interrupt.

- Can be expanded to 64 priority levels by cascading additional interrupts. Eight slave 8259s may be cascaded to a master 8259 to provide up to 64 priority levels.

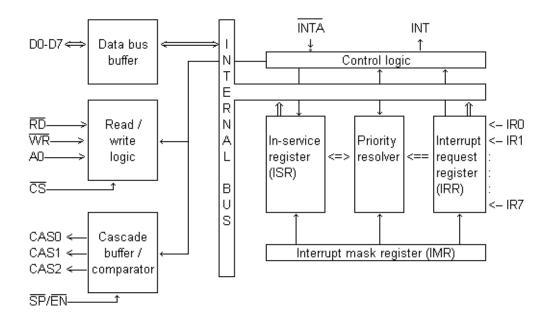

Figure 3.11: 8259 Internal Block Diagram

Figure 3.11 shows the internal block diagram of 8259. It includes eight blocks: control logic, read/write logic, data bus buffer, three registers (IRR, ISR, and IMR), priority resolver and cascade buffer.

| 20         | 4  |      | 20 | l.v   |

|------------|----|------|----|-------|

| <u>_CS</u> |    |      | 28 | Vcc   |

| WR         | 2  |      | 27 | AD    |

| RD         | 3  |      | 26 | INTA  |

| D7         | 4  |      | 25 | IR7   |

| D6         | 5  |      | 24 | IR6   |

| D5         | 6  |      | 23 | IR5   |

| D4         | 7  | 8259 | 22 | IR4   |

| D3         | 8  | PIC  | 21 | IR3   |

| D2         | 9  |      | 20 | IR2   |

| D1         | 10 |      | 19 | IR1   |

| DO         | 11 |      | 18 | IRO   |

| CASO       | 12 |      | 17 | INT   |

| CAS1       | 13 |      | 16 | SP/EN |

| gnd        | 14 |      | 15 | CAS2  |

Pin Diagram of 8259

- A0: Address input line, used to select control register.

- CAS 0 CAS 2: Bi-directional, 3 bit cascade lines. In master mode, PIC places slave ID number on these lines. In slave mode, the PIC reads slave ID number from master on these lines. It may be regarded as slave-select.

- SP/EN (slave program / enable): In non-buffered mode, it is SP- input, used to distinguish master/slave PIC. In buffered mode, it is output line used to enable buffers

- INT: Interrupt line, connected to INTR of microprocessor.

### **Interrupt Operation**

The Interrupt Enable (IE) flip-flop is enabled by writing the EI instruction. The 8259 is initialized by writing control words in the control register: Initialization Command Words (ICWs) and Operational Command Word (OCWs). ICWs are used to specify interrupt vector address. OCWs perform masking of interrupts, status read operation. After 8259 is initialized, the following sequence of events occurs when one interrupt request line go high:

- The IRR stores the request.

- The priority resolver checks three registers: the IRR, IMR, ISR. It resolves the priority and sets the INT pin high.

- The processor acknowledges the interrupt by sending INTA.

- After INTA is received, the priority bit in the ISR is set, the corresponding bit in IRR is reset. Then the opcode for the CALL instruction is placed on the data bus.

- When the processor decodes the CALL instruction, it places two more INTA signals on the data bus.

- When the 8259 receives the second INTA, it places the low order byte of the CALL address on the data bus. At the third INTA, it places the high-order byte on the data bus. This address is placed in the control register during initialization.

- During the third INTA, the ISR bit is reset.

- The program sequence is transferred to specified CALL address.

### ICW1 (Initialization Command Word 1):

ICW1 specify lower byte of ISR CALL address.

| A0 | D7 | D6 | D5 | D4 | D3   | D2  | D1   | D0  |

|----|----|----|----|----|------|-----|------|-----|

| 0  | A7 | A6 | A5 | 1  | LTIM | ADI | SNGL | IC4 |

D0: IC4: 0=no ICW4, 1=ICW4 required

D1: SNGL: 1=Single PIC, 0=Cascaded PIC

D2: ADI: Address interval used only in 8085, not 8086. 1=ISR's are 4 bytes apart (0200, 0204, etc)

0=ISR's are 8 byte apart (0200, 0208, etc)

D3: LTIM: level triggered interrupt mode: 1=All IR lines level triggered, 0=edge triggered

D4-D7: A5-A7: 8085 only. ISR address lower byte segment.

The lower byte is

A7 A6 A5 A4 A3 A2 A1 A0

of which A7, A6, A5 are provided by D7-D5 of ICW1 (if ADI=1), or A7, A6 are provided if ADI=0. A4-A0 (or A5-A0) is set by 8259 itself:

|     | ADI-1 (Spacing + bytes) |    |    |    |    |    |    |    |  |  |  |  |  |

|-----|-------------------------|----|----|----|----|----|----|----|--|--|--|--|--|

| IRQ | A7                      | A6 | A5 | A4 | A3 | A2 | A1 | A0 |  |  |  |  |  |

| IRO | A7                      | A6 | A5 | 0  | 0  | 0  | 0  | 0  |  |  |  |  |  |

| IR1 | A7                      | A6 | A5 | 0  | 0  | 1  | 0  | 0  |  |  |  |  |  |

| IR2 | A7                      | A6 | A5 | 0  | 1  | 0  | 0  | 0  |  |  |  |  |  |

| IR3 | A7                      | A6 | A5 | 0  | 1  | 1  | 0  | 0  |  |  |  |  |  |

| IR4 | A7                      | A6 | A5 | 1  | 0  | 0  | 0  | 0  |  |  |  |  |  |

| IR5 | A7                      | A6 | A5 | 1  | 0  | 1  | 0  | 0  |  |  |  |  |  |

| IR6 | A7                      | A6 | A5 | 1  | 1  | 1  | 0  | 0  |  |  |  |  |  |

| IR7 | A7                      | A6 | A5 | 1  | 1  | 1  | 0  | 0  |  |  |  |  |  |

ADI=1 (spacing 4 bytes)

ADI=0 (spacing 8 bytes)

| IRQ | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|-----|----|----|----|----|----|----|----|----|

| IRO | A7 | A6 | 0  | 0  | 0  | 0  | 0  | 0  |

| IR1 | A7 | A6 | 0  | 0  | 1  | 0  | 0  | 0  |

| IR2 | A7 | A6 | 0  | 1  | 0  | 0  | 0  | 0  |

| IR3 | A7 | A6 | 0  | 1  | 1  | 0  | 0  | 0  |

| IR4 | A7 | A6 | 1  | 0  | 0  | 0  | 0  | 0  |

| IR5 | A7 | A6 | 1  | 0  | 1  | 0  | 0  | 0  |

| IR6 | A7 | A6 | 1  | 1  | 0  | 0  | 0  | 0  |

| IR7 | A7 | A6 | 1  | 1  | 1  | 0  | 0  | 0  |

### ICW2 (Initialization Command Word 2):

ICW2 specify higher byte of ISR CALL address (8085), or 8 bit vector address (8086).

| A0 | D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 |

|----|-----|-----|-----|-----|-----|-----|----|----|

| 1  | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 |

#### ICW3 (Initialization Command Word 3):

ICW3 is required only if several 8259's are used in cascaded form.ICW3 can operate in master mode and slave mode.

| A0 |        | D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0  |

|----|--------|----|----|----|----|-----|-----|-----|-----|

| 1  | Master | S7 | S6 | S5 | S4 | \$3 | S2  | S1  | S0  |

|    | Slave  | 0  | 0  | 0  | 0  | 0   | ID3 | ID2 | ID1 |

- Master mode: 1 indicates slave is present on that interrupt, 0 indicates direct interrupt

- Slave mode: ID3-ID2-ID1 is the slave ID number. Slave 4 on IR4 has ICW3=04h (0000 0100)

### ICW4 (Initialization Command Word 4)

| A0 | D7 | D6 | D5 | D4   | D3  | D2  | D1   | D0   |

|----|----|----|----|------|-----|-----|------|------|

| 1  | 0  | 0  | 0  | SFNM | BUF | M/S | AEOI | Mode |

• SFNM: 1=Special Fully Nested Mode, 0=FNM

- M/S: 1=Master, 0=Slave

- AEOI: 1=Auto End of Interrupt, 0=Normal

- Mode: 0=8085, 1=8086

# OCW1 (Operational Command Word 1)

OCW1 specify masking of interrupts.

| A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|----|

| 1  | M7 | M6 | M5 | M4 | M3 | M2 | M1 | M0 |

IRn is masked by setting Mn to 1; mask cleared by setting Mn to 0 (n=0..7)

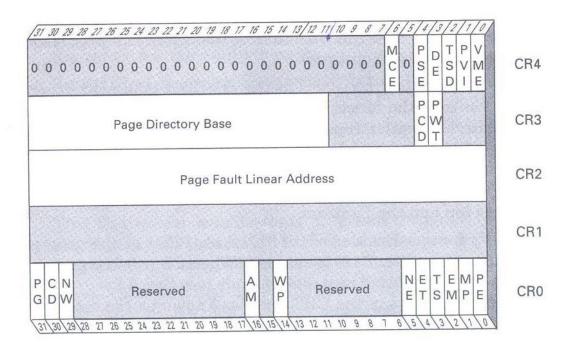

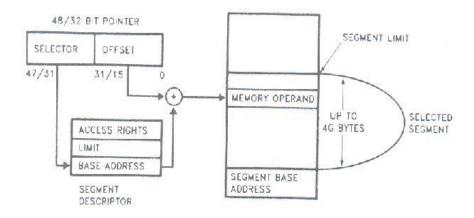

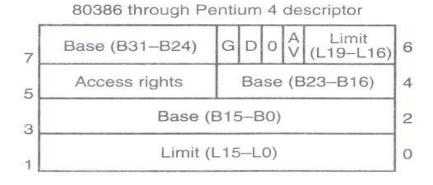

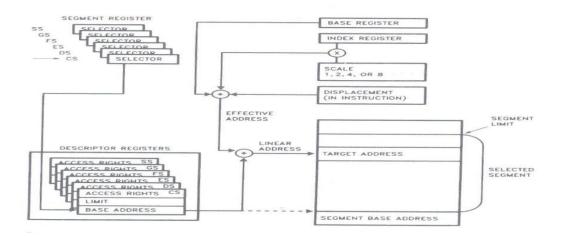

# OCW2 (Operational Command Word 2)